[시스템 소개]

이 스위트룸은 TMS320F2812 + ep2c8q208c8의 DSP + FPGA + NIOS 학습 및 개발 플랫폼을 기반으로하여 TMS320F2812 및 ALTERA CYCLONE ii의 유연성과 강력한 기능에 대한 완벽한 플레이를 제공합니다. 개발 키트 사용자 설명서는 자세히 이해하기 쉽고 많은 소스 코드가 시작되기 쉽습니다 (dsp와 FPGA 2 부품으로 나뉘어져 있음). 우리는 사용자를 완전한 FPGA IP 핵심을 제공합니다, 체계는 IP 커널을 통해서 할당되고 연결되고, 사용자는 필요에 따라 기능을 자르거나 추가할 수 있습니다. 우리의 주변 장치는 FPGA 및 DSP 연결, 레벨 변환, 버스 격리 및 중재와 같은 첨단 기술이기 때문에, 이 구조 시스템 때문에 매우 편리하고 유연하며 간결합니다. 따라서 달리고 안정되어 있고, 모는 현재, 지연을 조정할 수 있습니다, 필요조건에 따라 각 입력/출력 항구의 산출 수준 기준. 그것은 고속, 높은 안정되어 있는 DSP + FPGA 신청을 위한 cycloniii 그리고 pll의 많은 IP 핵심의 전 사용을 만들 수 있습니다, 또한 ALTERA DSP 빌더를 사용하여 하나 이상의 DSP IP 코어를 생성하여 다중 코어 cpu의 응용 시스템을 형성 할 수 있습니다. 이 자원은 일반적인 cpld에 의해 유효하지 않습니다. 이 구조는 fpga의 융통성, 강한 성과 및 TMS320F2812 부유한 자원에 가득 차있는 놀이를 줍니다. 수동 배선 디자인을 위한 고주파 배선 체계에 따라 직업적인 고위 엔지니어를 통해서 발달 널, 체계 반대로 방해 및 반복 문제의 가득 차있는 고려, 그래서 가동 및 안정성. 초보자를위한 첫 번째 선택이며 f2812와 fpga를 배우는 연구에 종사하는 연구원입니다.

이 개발 보드는 초보자가 배우고 사용하는 것입니다. 그것은 또한 사용자가 제품 개발 주기를 단축하기 위하여 2개의 발달을 만드는 시스템 널으로 사용자의 제품으로 끼워넣어질 수 있습니다.

[시스템 자원]

DSP 프로세서 TMS320F2812, 32 비트 고정 포인트 고속 디지털 프로세서, 150 m의 가장 높은 작동 주파수;

칩에 내장 된 128K * 16 비트 플래시는 사용자 프로그램을 편리하게 응고하는 데 사용할 수 있으며 플래시가 암호화 될 수 있습니다.

18K * 16 조금 SRAM 영화에서 건축됩니다.

4K * 16 조금 시동 rom은 칩에서 건축됩니다.

1K * 16 조금 OTP rom은 칩에서 건축됩니다.

확장 256K * 16 비트 SRAM, IS61LV25616;

512K * 16 비트 플래시, SST39VF800 확장 사용자가 더 큰 프로그램을 구울 수 있도록;

2 8 세그먼트 디지털 방식으로 관;

8 LED 발광 튜브, 편리한 상태 표시;

9 독립 버튼은 뽑아.

1 부저;

실험을 위한 pc에 연결될 수 있는 1 RS-232 공용영역.

1 방법 RS-485 공용영역, 편리한 사용자 네트워킹, 항구 보호 측정;

1 CAN2.0 인터페이스, 편리한 사용자 네트워킹;

16 AD 입력 인터페이스 (입력 범위 0 ~ 3V), 첫 번째, 두 번째는 검증 실험, 3, 4 입력 플러스 리미터 및 앰프 다음 처리, 입력 범위 0 ~ 3V (주의는 범위를 초과해서는 안됩니다!) ;

4 DA 출력 인터페이스;

1 USB 2 장치 인터페이스, 계획은 성숙한 CY7C68013 칩이며, 기성품 펌웨어를 제공하고 PC 통화 예 코드는 pc와 쉽게 통신 할 수 있으며 두 가지 개발을 수행합니다.

이어폰 잭은 쉽게 재생 기능을 깨달을 수 있습니다.

마이크 소켓은 편리하게 기록을 위해 사용될 수 있습니다.

12864 중국어 그래픽 LCD 인터페이스;

1602 문자 LCD 인터페이스;

1 EEPROM, 칩 24lc64의 IIC 버스를 가진 자료 전송 실험;

DC 모터 제어 인터페이스, 안티 플러그 디자인;

단계 모터 통제 공용영역, 반대로 마개 디자인;

SPI 인터페이스, 편리한 네트워킹;

모든 PWM 출력 인터페이스를 추출하고 사용자는 특정 요구 사항에 따라 사용할 수 있습니다.

2 도로의 외부 확장을위한 비 차폐 인터럽트 소스 입력 인터페이스.

그것은 확장 5 채널 interruptable 소스 입력 인터페이스, 1 그들 의해 키.

최대 16 입력 및 14 출력 인터페이스, 사용자가 증가하고 우리가 제공하는 FPGA IP 코어를 수정하여 확장 I/o의 수를 삭제할 수 있습니다.

버스는 개방적이고, 데이터 라인, 주소 라인, 제어 라인 및 특수 기능 핀은 사용자가 두 번 개발하는 데 편리한 모든 led입니다.

+ 5V, 3.3V, GND 및 다른 힘 시험 점;

전력 공급은 외부 전압 규칙에 의해 직접 공급됩니다.

독립적인 스위치, 통제 전력 공급, 편리한 가동;

4개의 조정 구멍은 사용자를 설치하고 고치는 것이 편리합니다.

FPGA 및 DSP 인터페이스를 통해 2 디지털 튜브.

FPGA 및 DSP 인터페이스를 통해 8 키 입력.

인터럽트 소스 입력 인터페이스가 제공됩니다.

그것은 쉬운 디버깅을 수동 자동 리셋 회로를 제공합니다.

버스 오픈, 데이터 라인, 주소 라인, 제어 라인, 특수 기능 핀 모든 리드 아웃, 편리한 사용자 두 번 개발.

부저.

전원 공급 장치는 점퍼 또는 USB 인터페이스로 선택할 수 있습니다.

1 독립 릴레이 각 릴레이는 일반적으로 열리고, 전기 충격 되었습니다 elicited 사용자 편의.

새로운 알테라 cylconeII FPGA ep2c8q208c8는 dsp와 공용영역하고 의사 소통하기 위하여 이용되고, I/O 항구의 연장은 따로따로 밖으로 singled.

논리 세포: 8256

I/O: 139

레지스터: 8745

차동 I/O 쌍. 62

메모리 비트: 165888

M4K RAM 블록: 36

속도 등급: 8

Pll: 2

FPGA 윤곽 칩 EPCS16 16M 조금은 윤곽 필요조건의 대부분을 만날 수 있습니다.

SDRAM 8M X16bit 16M 바이트 기억은 모아진 임시 자료를 저장할 수 있습니다. 또는 NIOS 실험의 데이터 저장을하십시오.

[지원 정보 및 소프트웨어]

1. 완전한 도식 도표 (pcb와 일치하기 위하여 보장되는 PDF 체재) 는, 빨리 다수 실제적인 공용영역의 신청을 파악합니다.

2. 모든 실험은 C 언어 근원 부호를 제공하고, 상세한 중국 주석을 비치하고 있습니다.

3. 온라인 불타는 섬광의 방법 및 공구는 사용자의 자신의 프로그램을 고형화하기 위하여;

4. 칩 설명서: 발달 널에 모든 칩에 칩 정보를 제공하십시오;

5. send 원래 TI DSP 개발 환경 CCS3.3;

6. 에뮬레이터 드라이버 및 기타 DSP 책 및 CD-ROM 관련 학습 자료를 제공합니다.

7. Acrobat 리더, Bushound USB 버스 모니터링 소프트웨어, Sscom 직렬 디버깅 보조 및 기타 디버깅 도구.

8. Altera 다운로드 선 도표를 보내기 위하여;

9. 액정 글꼴 소프트웨어를 주십시오;

10. 교부금 tcp/ip 계약 양: 양 1 ~ 3;

11. USB 사양 문서를 제공;

12. CAN2.0 명세 문서를 주십시오;

13. U 디스크 시스템 설명 문서를 제공;

14. FAT16, FAT32 시스템 문서 제공;

15. UCOS-II f2812의 이식원의 원천을주십시오.

16. FFT, FIR 및 기타 계산 라이브러리를 제공하십시오.

17. TI 가득 차있는 칩 포장 라이브러리를 주십시오.

18. 사용자 설명서: 회로 분석, 부호 소개, CCS2000 빠른 시작 지도, 등을 포함하여 아주 상세한.

QUARTUS 8.0 + NIOS II IDE 개발 환경 완전히 금이 버전.

VHDL 일상적인 컬렉션

VHDL 자습서

VERILOG 루틴의 135 사례

VERILOG 자습서

DSPbuilder 자습서

RS232 개발을위한 직렬 청취자 소프트웨어 보내기

LCD 디스플레이 프로그램의 글꼴 추출 소프트웨어 및 개발

USB2.0 호스트 컴퓨터 프로그램 및 소스 코드

완벽한 FPGA 시스템 리소스는 IP 코어와 소스 코드를 할당합니다.

많은 수의 완전한 NIOS 개발 자습서. DSP, EDA, SOPC 비디오 자습서를 포함하여. DSP, FPGA, SOPC 시스템 개발을 쉽게 마스터하게하십시오.

위의 정보는 상업 용도뿐만 아니라 연구를위한 것입니다.

실험 가이드 북 다운로드! (그것을 저장하려면 오른쪽 버튼을 클릭)

[코드 및 관련 실험]

PC 엔드 데모 코드

PC 엔드 코드의 프로그래밍 언어는 Borland C + builder의 그래픽 인터페이스를 제공합니다. DLL 라이브러리 기능을 호출하여 사용자는 USB 데이터를 수신하고 수신하는 방법을 설명했습니다. 동일한 DSP 엔드 코드는 데이터를 읽고 쓰는 방법을 보여줍니다. 사용자는 신속하게 그것을 사용하지 않고 자신의 프로그램 개발을 완료하기 위해이 전화 예를 참조 할 수 있습니다. USB 프로토콜의 세부 사항을 처리하십시오.

USB2.0 상단 컴퓨터 데이터 전송 제어 실험 (상단 컴퓨터 소스 코드 제공, 시스템 개발 및 응용 프로그램에 쉽게 투자 할 수 있도록)

FPGA IP 드라이버 및 소스 코드 완료

전체 시스템 로직 통합 및 시스템 자원 할당, 사용자는 자신의 요구 및 응용 프로그램에 따라 수집 할 수 있으므로 fpga에 의해 연결된 시스템 자원은 해당 읽기 및 쓰기 주소를 가지고, 그리고 완전한 SDRAM IP 중핵, 사용자는 큰 수용량 체계 자료 저장을 위해 사용할 수 있습니다 제공합니다, 회사는 또한 체계를 사용자에게 제공할 것입니다. 더 높은 품질과 저렴 한 고속 AD/DA 확장, TFT LCD 확장, 광 커플러 절연 큰 전류 I/O 모듈, Wah Sheng EDA 웹 사이트에주의를 기울이십시오.

FPGA 부품:

(VHDL 부호를 채택하고, VHDL 일상적인 수집, 700 이상 통용되는 루틴을 제공합니다. VERILOG 일상적인 135 사례, 많은 압축 개발 및 학습 자료, 볼 수있는 방법을 완료 할 수 없습니다!!! 사용자의 참고를 위해.

더 많은 실험과 비디오 자습서가 시작됩니다. Hua Sheng EDA 웹 사이트에주의를 기울이십시오.

[표준 구성]

1, DSP 2812 개발 보드 원피스

2, 5V/1A 스위치 전원 공급 장치

3, USB2.0 케이블 1

4, RS232 통신 라인 1

5, LCD1602 액정 1

6. 1 DC 모터

7. 1 DVD CD-ROM CD-ROM

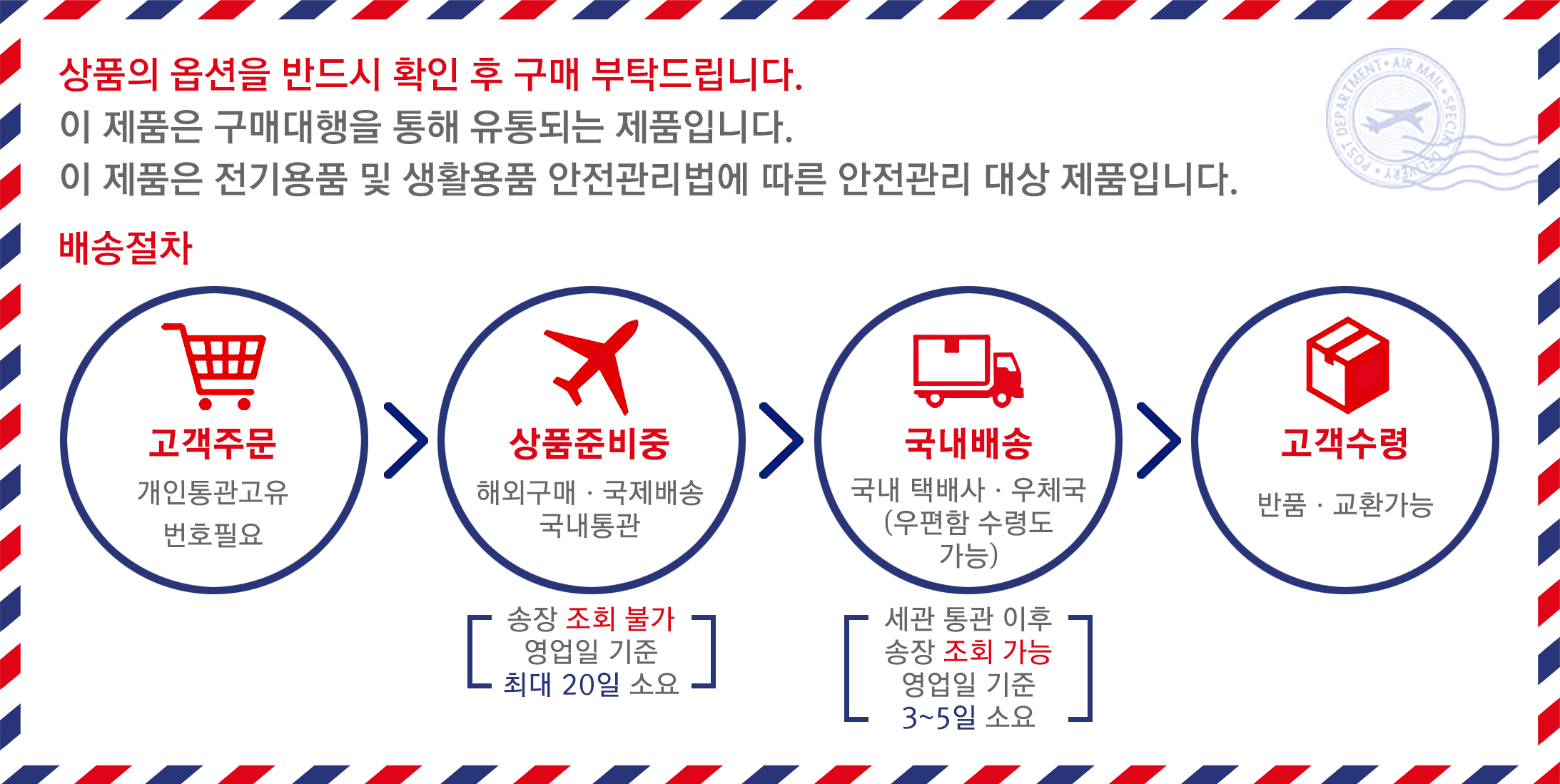

배송기간

배송기간